# HEWLETTPRACKARD JOURNAL

# 06301 25KV 0.5U

### **HEWLETT·PACKARD JOURNAL**

Technical Information from the Laboratories of Hewlett-Packard Company

AUGUST 1982 Volume 33 • Number 8

#### **Contents:**

Viewpoints-IC Process Technology: VLSI and Beyond, by Frederic N. Schwettmann and John L. Moll The demand for ever-smaller device dimensions requires continual advances in IC fabrication techniques. Here's where we stand today.

Optical IC Lithography Using Trilayer Resist, by Michael M. O'Toole, E. David Liu, and Gary W. Ray Using three layers minimizes exposure variations caused by bulk and standing-wave effects.

Silicon Integrated Circuits Using Beam-Recrystallized Polysilicon, by Theodore I. Kamins Heating a thin layer of polysilicon to the melting point and letting it cool improves its characteristics for device fabrication.

X-Ray Lithography, by Garrett A. Garrettson and Armand P. Neukermans Soft X-ray radiation shows promise as the next step in the evolution of VLSI circuit lithography.

Dry Etching: An Overview, by Paul J. Marcoux Replacing liquid etching processes with plasma etching techniques improves control over etch direction and endpoint detection.

Thin Films Formed by Plasma-Enhanced Chemical Vapor Deposition, by Dragan B. Ilic Lower CVD process temperatures can be used with this approach.

Electromigration: An Overview, by Paul P. Merchant This IC conductor failure mechanism can be a limiting factor to shrinking VLSI circuit dimensions.

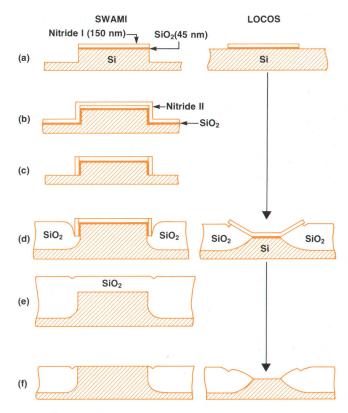

SWAMI: A Zero-Encroachment Local Oxidation Process, by Kuang Yi Chiu This process minimizes lateral oxidation which alters critical device dimensions and limits circuit density.

High-Pressure Oxidation, by William A. Brown Increasing the pressure of the oxidizing gas reduces the time and temperature required for a silicon oxidation cycle.

#### In this Issue:

The application of silicon integrated circuits has become pervasive in almost all human activities. It is expected that this pervasiveness will continue to expand at least through the end of this century, characterized by higher and higher levels of integration-more and more transistors in the same silicon area. We are entering the era of VLSI-very large-scale integration—which means hundreds of thousands of devices on a single chip of silicon. One of the key driving forces behind this trend is the rapid, exhilarating development of the process technologies required for fabricating VLSI circuits. Remarkable advances have been im-25KU 0.5U plemented in manufacturing that were believed to be impossible a few short years ago.

In this issue, a number of the process technologies currently being explored at Hewlett-Packard are de-

scribed. The strong interdisciplinary nature of these evolving technologies is readily apparent and will be more extensive in the future. With critical dimensions in some cases approaching several atomic layers, the intricacy of these processes is increasing and we will in the next 5 to 10 years begin to see the limits of some technologies defined and perhaps approached. Until then, the cramming of more features on a chip to get higher performance with less power dissipation will continue at a rapid pace.

Cover: A solarized version of Fig. 8, page 8.

-Frederic N. Schwettmann, Guest Editor

Editor, Richard P. Dolan

Associate Editor, Kenneth A. Shaw

Art Director, Photographer, Arvid A. Danielson

Illustrator, Nancy S. Vanderbloom Administrative Services, Typography, Anne S. LoPresti, Susan E. Wright • European Production Supervisor, Henk Van Lammeren

### **IC Process Technology: VLSI and Beyond**

#### by Frederic N. Schwettmann and John L. Moll

HE VLSI ERA is here. Integrated circuits containing over 100,000 devices with 1-to-2-micrometer feature sizes have become a manufacturing reality. A prime example of the power of this technology is the demonstration of a 450,000-device, 32-bit microcomputer operating at a clock rate of 18 MHz.<sup>1</sup> This remarkable accomplishment is the result of the congruence of advances in design automation, process technology, packaging and testing. In the field of process technology, significant achievements have been demonstrated in lithography, etching, interconnections, materials and low-temperature processing. Now that VLSI has become a reality, where and how far the technology can be extended are key questions facing researchers the world over.

#### **Device Scaling**

The presently available processing capability of defining dimensions as small as 1 to 1.5 micrometers will be driven down to even smaller sizes. The general device performance guideline of constant-field scaling\* has been followed as metal-oxidesemiconductor (MOS) device dimensions are reduced, but with significant violations. The average voltage drop per micrometer along the device channel has increased somewhat, and the maximum electric field in the gate dielectric has increased. In addition, the channel length has decreased faster than the junction depths for the source and drain regions. The result is that from time to time new physical phenomena need to be included in describing device operation and electrical characteristics, and in determining the sensitivity of circuit operation to process variations.

Up to this time, scaling of both lateral and vertical dimensions has been advantageous, both to functional integration and to circuit performance. As the dimensions become less than one micrometer the performance advantage will become more difficult to maintain. Parasitic resistance will increase, and as chips become more complex, parasitic capacitance will be more difficult to control. A lower operating voltage tends to reduce noise margin and places greater demands on process control. There is in fact a probability that at some minimal dimension, performance will peak, limited by parasitic effects and unscalable parameters such as operating temperature and subthreshold conduction.

An often asked question is "What are the minimum usable line and space sizes for silicon VLSI?" A proposed answer for the minimum feature, both in an MOS device and in interconnect lines, is approximately 0.25 micrometer. Thermodynamic and quantum-mechanical effects begin to limit device and circuit performance at sufficiently small dimensions. There are more pragmatic considerations, such as the previously mentioned parasitic effect on performance, and limitations in the perfection and control of fabrication processes. The cost of building and maintaining a facility to achieve the necessary degree of control for submicrometer VLSI will certainly far exceed present-day factory costs.

There are still a number of "aces in the hole" that make the ultimate scaling and performance of silicon VLSI a moving target. The discussion to this point has centered around MOS switches built in the self-aligned silicon gate configuration. There are possible process inventions that could, for example, significantly reduce the parasitic and interconnect limits (see article on page 31 and box on page 33). Device inventions such as multilevel films of active

\*Constant-field scaling means that if, when the physical dimensions of a device are reduced, the operating voltages and currents are also reduced so that the electric fields within the device remain constant, performance should remain the same. In practice this is difficult to do because of the need for a standard operating voltage.

devices could also affect system architecture. There is so much activity in both new processes and new device configurations that any attempt to report all of the efforts would fall far short of the mark.

#### Lithography

The dominant lithographic technology currently used in IC manufacturing is the 1:1 optical projection printer. This tool allows geometries as small as two micrometers and affords high wafer throughput. Below two micrometers, the trend has been to stepand-repeat exposure systems. In addition to better resolution, these tools provide greater alignment accuracy. As a general guideline, the layer-to-layer registration is targeted to be no worse than 0.25 times the minimum resolvable feature size. Therefore, for a 1- $\mu$ m technology, the layer-to-layer registration should be better than  $\pm 0.25 \ \mu m$ , a value well within the capability of a state-of-the-art step-and-repeat system. It is expected that as the numerical aperture of the lenses used in the optical system is increased and the wavelength of the exposing light is decreased, a real limit of 0.5  $\mu$ m for refractive optics will be approached. Crucial to the success of optical systems in the submicrometer regime is the use of a multilayer resist technology (see article on page 5). Much effort is being expended in this area to extend the usable range of optical systems. Higher contrast resists such as those using inorganic materials may ultimately replace the organic photoresists now in common use.

At 0.5 micrometer and smaller, X-ray and electron beam lithography are the contenders. Electron beam has demonstrated fineline capability and possesses excellent alignment potential. However, throughput is currently lower than for optical systems and the cost is considerably higher. X-ray, on the other hand, has excellent resolution capability and the potential for higher throughput (see article on page 14). For dimensions less than 0.5 micrometer, stepand-repeat systems would be required to achieve the desired overlay accuracy. This eases the mask fabrication problems, but requires that a more intense source of X-rays be used and/or a more sensitive resist developed. Clearly, much technological progress is required.

#### Etching

Once a pattern has been defined in the resist, it must be faithfully reproduced in the underlying layer. Before the advent of VLSI, etching was usually done with wet chemistry. This technology almost always has the virtue of nearly infinite selectivity (ability to etch one material without affecting another material), but is isotropic. For geometries greater than two micrometers, this is not a significant problem. However, when etching a 1- $\mu$ m-wide pattern in a layer that is 0.5- $\mu$ m thick, the lateral portion of isotropic etching completely destroys the pattern. For most VLSI applications and all future submicrometer work, anisotropic etching will be essential. The use of dry plasma processes has emerged as the primary etch technology (see article on page 19).

The transition from wet to dry etching has been difficult. The required equipment (see box on page 22) is more complex, more expensive and has lower wafer throughput when compared to wet etching. In addition to anisotropy and good selectivity, sloped sidewalls are required to provide conformal step coverage for subsequent layers. The task is to find the right combination of gases and process conditions to match the requirements. An enduring significant problem is the lack of understanding of the mechanisms associated with anisotropy, etch rate and selectivity. Much work is required in this area.

#### Interconnections

As the speed of individual devices increases, the time delays associated with the interconnections begins to play a significant role in circuit performance. As the minimum feature size is decreased, the area of the interconnect and the contact area become smaller. The time delay is dependent on the resistance of the interconnections and the capacitance controlled primarily by the dielectric layer. The dielectric material in most cases is either silicon dioxide or silicon nitride.

For the device interconnections, a variety of materials are available. Refractory metal silicides on top of polysilicon are gradually replacing polysilicon as a first-level interconnect material. An order-of-magnitude decrease in resistivity is gained by this approach. More emphasis is now being placed on two levels of metallization on top of the polysilicon or polycide layer. This provides greater flexibility for the circuit designer, but adds to the manufacturing difficulty. Three or more levels of metallization are expected to become more common as experience is gained. Aluminum alloy metallization is currently used in almost all VLSI applications. As contacts to diffused areas with shallower junctions are required, barrier layers such as tungsten will be added to prevent spiking\* through the junctions. To decrease the contact resistance (contact area decreases, and hence resistance increases as the square of the scaling factor), silicide layers such as platinum silicide may be required.

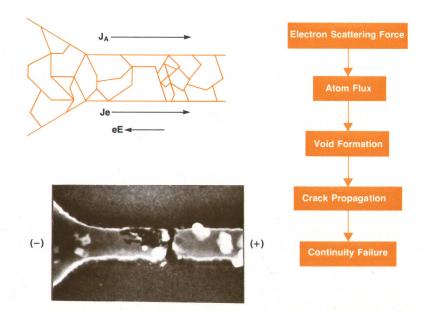

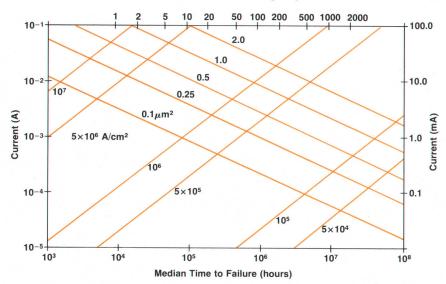

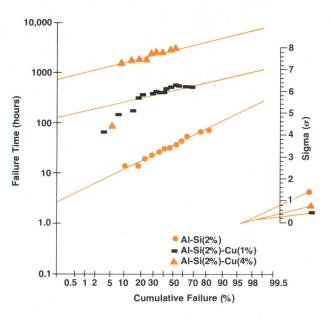

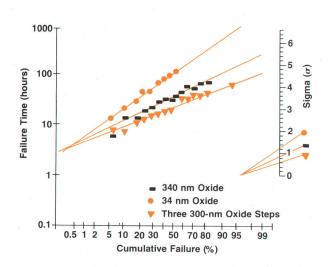

An additional factor, electromigration (see article on page 28), becomes important for circuit reliability as the conductor crosssectional area decreases and current density increases. This requirement may result in the replacement of aluminum alloys with materials such as tungsten. However, the higher resistivity of tungsten, about four times higher, results in another tradeoff between performance and reliability.

#### **Materials**

Another area expected to be of great concern in the submicrometer region is the silicon material itself. Already great care is being given to tighter control on the specifications of substrates. The amount, distribution and chemical bonding of silicon impurities such as oxygen and carbon are being carefully monitored and their effect on device performance evaluated. The coupling of these species to the defects generated during processing is a major concern. A variety of gettering schemes are being studied and implemented where needed. The tools for characterizing defects on a near-atomic level, such as scanning transmission electron microscopy (STEM), are now available and are being brought to bear on the problems with remarkable results. There is much optimism on being able to understand and control the location of defects in silicon.

One novel approach to forming a substrate, discussed in the article on page 10, is the use of an intense laser or electron beam to melt a polysilicon layer and then let it cool and recrystallize into large-grain polysilicon suitable for device fabrication.

#### Low-Temperature Processing

The requirements of shallow junctions in scaling and the need for the minimum lateral motion of dopants requires that processing temperatures be kept as low as possible. Instead of applying energy to deposition and growth processes by thermal means alone, plasma excitation will be used (see article on page 24). Already, deposition of silicon dioxide and silicon nitride by plasma techniques is available for manufacturing processes. Films deposited using plasma excitation tend to exhibit better step coverage than purely thermally deposited films. Interest is now high in

\*Enhanced diffusion of the contact metal in a localized area of the underlying semiconductor material resulting in an electrical short across a device junction. being able to deposit conducting materials such as aluminum and tungsten using plasma techniques.

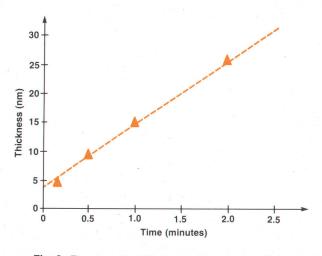

The growth of thin films in a plasma as opposed to deposition is a new and exciting area. Gate dielectrics of silicon nitride and nitrided silicon dioxide show promise for scaled devices requiring dielectric layers less than 10 nm thick (see box on page 26). They exhibit better physical durability, lower etch rates and lower defect densities. Much work needs to be done to understand the growth mechanisms and implement these films in the manufacturing environment.

• Another approach that will be useful in lowering processing temperatures is high-pressure oxidation (see article on page 34). This could be a useful tool in the submicrometer regime.

In summary, while design tools are still lagging the available process technology, the march toward smaller devices and circuits continues at a furious pace. It is expected that by the turn of the century, the ultimate limits in silicon will have been clearly demonstrated and maybe attained. Many challenges remain and opportunity exists for contribution and innovations in almost all engineering disciplines in reaching this goal.

#### Reference

1. J. Beyers, et al. "A 32b VLSI Chip," Digest of Technical Papers, Vol. 24, IEEE International Solid-State Circuits Conference, February 1981, THAM 9.1.

#### Frederic N. Schwettmann

Fred Schwettmann is the director of HP's Integrated Circuit Laboratory. His work has resulted in over 20 publications and presentations related to IC technology, and three patents, two on semiconductor technology, the other on petrochemical processing. He joined HP in 1976 with several years of experience in semiconductor and petrochemical R&D. Fred is the national vice chairman of new technologies for the Electrochemical Society and a member of the VLSI program committee of the IEEE. He was born in Brooklyn, New York and studied chemical engineering at the City College of New York, earning a BS degree in 1961, at New York

University, earning an MS degree in 1964, and at City University of New York, earning a PhD degree in 1969. Fred is married, has two children, and lives in San Jose, California. He enjoys running, playing racquetball and basketball, and sports in general. During his college days, Fred was voted "All-American" in lacrosse and was selected as most-valuable player for two years.

#### John L. Moll

John Moll has been with HP since 1974, first as the director of technology for the IC lab, and most recently as the manager of the ICSR lab and a senior scientist with HP Laboratories. He is well-known to circuit designers for the Ebers-Moll model of the large-signal behavior of transistors, has been on the faculty of Stanford University, and has extensive experience researching solid-state devices and the physics of solids. John's contributions have resulted in over 100 papers, ten patents, and a book, *Physics of Semiconductors*. He was a Guggenheim Fellow in 1964 and received the Howard N. Potts award from the Franklin Institute in 1967 and the Ebers

award from the IEEE in 1971. He is a Fellow of the IEEE and a member of the American Physical Society, National Academy of Engineering, and Sigma Xi.

# Optical IC Lithography Using Trilayer Resist

A composite photoresist layer reduces exposure effects that degrade pattern definition and reduce resolution in optical IC lithography.

#### by Michael M. O'Toole, E. David Liu, and Gary W. Ray

HE DENSITY AND PERFORMANCE of devices contained in today's VLSI circuits are primarily determined by the resolution capability of the lithographic technique used for the circuits' manufacture. The dominant technology uses an optical projection system to form an image of the desired pattern on the photoresistcovered surface of a silicon wafer. The theoretical image resolution limit of the lens systems in modern projection aligners is in the submicrometer range. However, the resolution obtainable in normal IC production is much poorer because of various resist and substrate surface effects.

To achieve dimensional control closer to the theoretical resolution limit of the projection system, a trilayer resist process has been developed. Before describing this process, it is useful to discuss the effects that degrade image resolution in conventional processing.

In an ideal situation, the image projected on a planar, nonreflective surface covered with positive resist will consist of perfectly dark lines, corresponding to the desired features, surrounded by evenly illuminated areas where the resist is exposed and later developed away. In typical IC fabrication, however, the image is projected onto a nonplanar reflective surface that is unevenly covered with resist. The nonplanar reflective surface provides the conditions for two effects that limit the usable resolution of a projection aligner. The bulk effect is caused by large thickness variations of the resist near abrupt changes (steps) in the surface topography. The standing-wave effect is caused by multiple reflections of the exposure illumination from the substrate surface.<sup>1</sup>

The bulk variation in the resist thickness as it covers a step is shown in Fig. 1. The resist layer on top of the step is thinner than it is next to the step and, in general, requires less exposure to be developed to the desired linewidth. As a result of the standing-wave effect, variations in the thickness of the resist or any thin semitransparent layers under the resist can cause large variations in the exposure energy coupled into the resist. This effect is periodic within the thickness of a layer. The period is  $\lambda/2n$ , where  $\lambda$  is the wavelength of the illumination and n is the index of refraction of 0.65 micrometer can cause a major exposure variation. Both effects are most evident for resist feature dimensions

\*Some of the data presented in this article has been previously discussed by the authors at the 1981 Symposium on VLSI Technology in Maui, Hawaii and in articles published in the November, 1981 issue of the IEEE Transactions on Electron Devices and the May, 1982 issue of Solid State Technology.

approaching the resolution limit of the projection lens.

The standing-wave and bulk effects may be studied by using a computer program for the simulation of optical projection printing.<sup>2</sup> The program assumes diffractionlimited optics, considers the numerical aperture of the imaging lens, the imaging wavelength, the partial coherence factor of the illumination system, and the focus error, and calculates the image intensity pattern for a specified feature on the surface of the resist. The exposure and development of the resist are calculated by using the model described by Dill, et al.<sup>3</sup> This model considers the substrate's topography and the characteristics and thickness of the resist. The final output is a simulated line edge profile in positive resist.

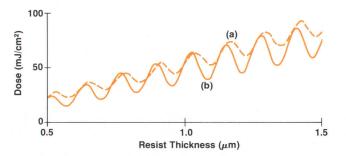

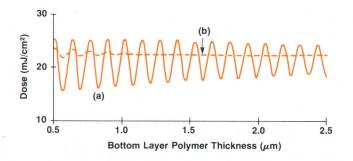

A sample output of the simulation program is given in Fig. 2, which shows the nominal exposure required for a periodic 1- $\mu$ m-wide line-and-space pattern as a function of positive resist thickness on (a) a silicon substrate, and (b) an aluminum substrate. The nominal dose is defined as the exposure energy density required to replicate the mask linewidth in the resist. The bulk effect causes the gradual rise of the curve, and the standing-wave effect causes the periodic variation. The period  $\lambda/2n$  is 128 nm for an exposure wavelength of 436 nm and a resist refractive index of 1.69. To compensate the standing-wave effect caused by a 64-nm thickness variation in a 1- $\mu$ m-thick layer of positive resist on a silicon substrate, a 25% exposure difference is required to cor-

**Fig. 1.** Resist step coverage: 1-µm-thick resist pattern over 0.5-µm-high step.

**Fig. 2.** The exposure energy density (dose) required at a wavelength of 436 nm to achieve 1- $\mu$ m-wide lines and spaces in HPR 204 positive resist on (a) silicon and (b) aluminum surfaces for numerical aperture NA=0.28, perfect focus, and partial coherence factor  $\sigma$ =0.7.

rect for the bulk effect caused by a 250-nm resist thickness variation. From curve b of Fig. 2, a bulk thickness variation of about 420 nm is equal to a standing-wave thickness variation of 64 nm. Both effects can combine near a step to produce a significant variation in the nominal exposure dose required, causing severe linewidth control problems. Fig. 3 shows a microphotograph of 1- $\mu$ m-wide lines and spaces patterned in a 1- $\mu$ m-thick layer of positive resist over two 0.5- $\mu$ m-high polysilicon lines. The resist linewidth is very unstable near the edge of the steps and narrower on top of the polysilicon lines than in the lower field areas around them.

**Fig. 3.** 1- $\mu$ m-wide lines and spaces in 1  $\mu$ m of resist over 0.5- $\mu$ m-high polysilicon steps.

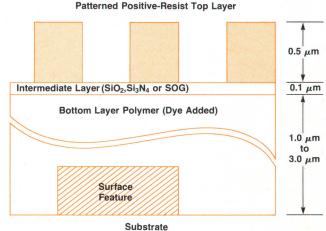

Fig. 4. Trilayer resist system.

#### **Trilayer Resist Process**

To realize the maximum resolution from a projection aligner, the surface of a wafer must behave as if it were planar and nonreflecting. In an attempt to achieve this condition, several multilayer resist processes have been recently proposed and demonstrated.<sup>4-9</sup> In a multilayer system, the substrate's topography is planarized by a thick bottom polymer layer. Optical reflections from the underlying surface topography can be eliminated by choosing an absorptive material for the bottom layer.

Fig. 4 illustrates the trilayer structure studied by Hewlett-Packard Laboratories. An absorbing polymer, one to three micrometers thick, is used to planarize the substrate topography. The planarized surface can be coated uniformly by the top resist layer, thus suppressing the bulk effect. The absorption of the exposure illumination by the bottom polymer layer eliminates reflections from the substrate topography and reduces the standing-wave effect. An intermediate inorganic layer serves as a mask during reactiveion-etching to transfer the top resist layer pattern to the bottom layer. The intermediate layer also prevents mixing of the top and bottom layer polymers.

Suitable materials for the bottom layer are polymers that planarize well. Transparent polymers may be made absorbing by adding dye. The dye must dissolve in the polymer and absorb strongly at the exposure wavelength. To simplify processing, the dye should be transparent at the alignment wavelength, allowing easy detection of the alignment mark through the thick bottom polymer layer.

Several materials have been used for the intermediate layer. Plasma-enhanced chemical-vapor deposition (PECVD) of silicon nitride done at room temperature is suitable (see article on page 24). Spin-on glass (SOG) has also been used as a suitable intermediate layer.<sup>10</sup> Because SOG can be applied by IC production equipment very similar to that used to apply resist, the use of SOG for the intermediate layer makes it easier to incorporate the trilayer process into an IC production facility. Both PECVD nitride and SOG permit rework of the top resist layer without having to strip the intermediate and bottom polymer layers.

Pattern transfer from the top resist layer to the inter-

mediate layer is achieved by plasma etching. If SOG is used for the intermediate layer, a  $CHF_3/CO_2$  gas mixture is used. The SOG pattern is transferred to the bottom polymer layer using an anisotropic oxygen plasma etch process.

The trilayer process was analyzed and optimized using simulations generated by the computer program mentioned earlier. Positive resist was used for the top and bottom layers and was developed using a conventional batch process. The exposure and development parameters for the positive resist were measured at Hewlett-Packard Laboratories<sup>11</sup> using equipment similar to Dill's for the exposure parameters and to Meyerhofer's<sup>12</sup> for the development parameters.

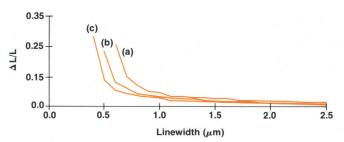

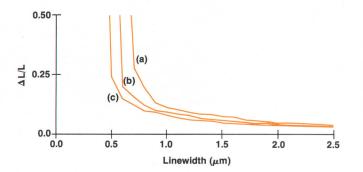

In addition to the optical parameters of the aligner and the exposure and development parameters of the resist, the computer simulation of the trilayer system considers the refractive indexes of the materials and thicknesses of the various layers. Fig. 5 shows the calculated nominal dose required to print 1- $\mu$ m-wide lines and spaces as a function of the thickness of the bottom polymer for the trilayer system of Fig. 4 on an aluminum substrate. Curve a assumes the absorption of HPR 204 positive resist and curve b assumes the absorption of this resist with dye added.

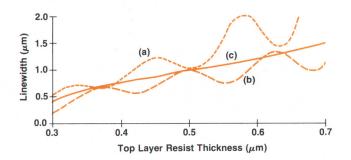

If the bottom polymer layer does not sufficiently planarize the substrate surface, the top layer of resist will disperse nonuniformly. Curves a and b of Fig. 6 show the calculated linewidth as a function of top resist thickness for two bottom polymer thicknesses of 1.03  $\mu$ m and 0.95  $\mu$ m. These two thicknesses represent the two extremes near 1  $\mu$ m of curve a in Fig. 5. In both cases, the simulated exposure dose has been adjusted to produce a  $1-\mu$ m-wide line for a  $0.5-\mu$ m-thick top resist layer. Both the bulk and standing-wave effects are clearly seen. If the top resist layer is uniformly 0.5- $\mu$ m thick, the nominal exposure required to maintain a one-micrometer dimension changes from 16 mJ/cm<sup>2</sup> for a 0.95- $\mu$ m-thick bottom layer to 25 mJ/cm<sup>2</sup> for a  $1.03-\mu$ m-thick bottom layer. This exposure variation is too great to achieve sufficient linewidth control over the entire wafer surface.

Adding dye to the bottom polymer of the trilayer process suppresses the standing-wave effect. Curve c of Fig. 6 shows the linewidth variation versus top resist layer thickness for a 1- $\mu$ m-thick bottom resist layer with dye added. The linewidth variation is caused entirely by the bulk ef-

**Fig. 5.** Nominal dose versus bottom polymer thickness for the trilayer system of Fig. 4 on an aluminum substrate using (a) HPR 204 positive resist and (b) HPR 204 containing 1.5% dye for the bottom polymer. Simulations are for 1- $\mu$ m-wide lines and spaces under perfect focus conditions.

**Fig. 6.** Simulated linewidth versus top resist layer thickness for 1- $\mu$ m-wide lines and spaces for (a) a 0.95- $\mu$ m-thick bottom layer of HPR 204 positive resist and an exposure dose of 16 mJ/cm<sup>2</sup> for the top layer of resist. (b) A 1.03- $\mu$ m-thick bottom layer of HPR 204 and a 21-mJ/cm<sup>2</sup> dose for the top layer. (c) When dye is added to a 1.0- $\mu$ m-thick bottom layer, the standing-wave effect on the linewidth in the top resist layer is eliminated.

fect. Because positive resist used for the bottom polymer has been shown to planarize well,<sup>13</sup> the top resist thickness can be held to close tolerance, and good linewidth control is expected.

#### **Experimental Results**

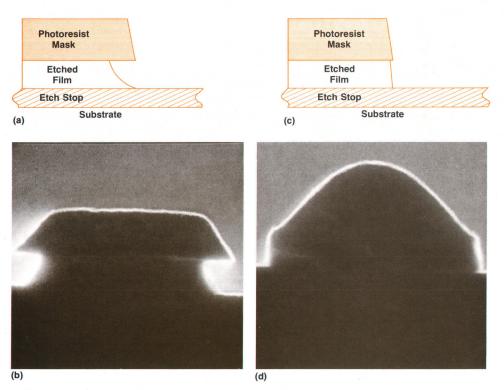

A resolution test mask was used to print lines and spaces over topography using the trilayer system and a direct-

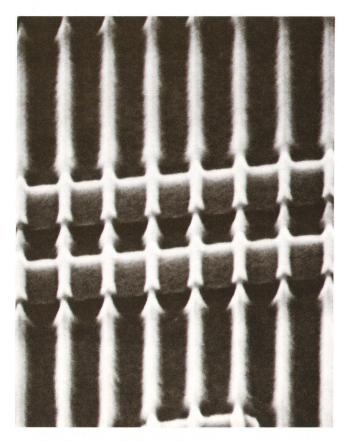

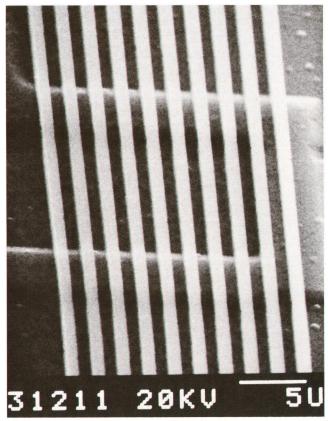

**Fig. 7.** 1-µm-wide lines and spaces in trilayer resist over 0.5-µm-high aluminum steps after reactive ion etch. 2.0-µm-thick HPR 204 positive resist containing 1.5% dye is used for the bottom polymer layer.

step-on-wafer (DSW) 10:1 optical projection aligner with a numerical aperture of 0.28 and an imaging wavelength of 436 nm. Fig. 7 shows a scanning-electron-microscope (SEM) microphotograph of 1- $\mu$ m-wide lines and spaces patterned with a trilayer process over 0.5- $\mu$ m aluminized topography. Because the 2.0- $\mu$ m-thick bottom resist layer planarizes the topography well, the thickness of the top resist layer is controlled to about  $\pm 0.03 \ \mu$ m. The bulk effect is minimized and the standing-wave effect is eliminated. Because the wafer surface appears planar and nonreflective, excellent linewidth control of 1- $\mu$ m-wide features over 0.5- $\mu$ m-high steps is achieved.

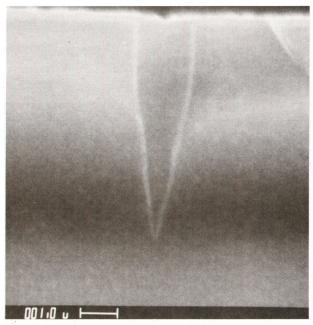

Fig. 8 shows the straight sidewalls that are possible with this process. The bottom and intermediate layers in Fig. 8 were etched in a single pumpdown using a reactive-ionetch system.

#### **Future of Optical Lithography**

Optical lithographic technology continues to evolve, both in equipment and in resist materials and techniques. Projection aligners with large numerical apertures, shorter imaging wavelengths, and better alignment capability are being designed. Future aligners<sup>14</sup> should have a theoretical resolution limit well into the submicrometer range and use sophisticated site-by-site autoalignment systems. In addition, new materials such as the inorganic resists<sup>6,7,15</sup> may be used in a multilayer resist system to further enhance the practical resolution of optical lithography.

**Fig. 8.** Edge profile of trilayer process using spin-on glass for the intermediate layer covering 1.0-μm-high aluminum steps. Profile is shown after reactive ion etching of bottom polymer layer.

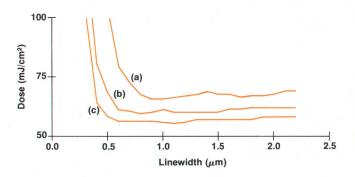

**Fig. 9.** The nominal exposure dose as a function of linewidth in micrometers for (a)  $\lambda$ =436 nm, NA=0.28; (b)  $\lambda$ = 405 nm, NA=0.35; and (c)  $\lambda$ = 240 nm, NA=0.25 ( $\sigma$ =0.7, all cases). Simulation parameters (see reference 11): A=0.57  $\mu$ m<sup>-1</sup>, B=0.08  $\mu$ m<sup>-1</sup>, C=0.01 cm<sup>2</sup>/mJ, F<sub>1</sub>=0.179, F<sub>2</sub>=-0.346, F<sub>3</sub>=0.168.

In an ideal multilayer resist system, one where planarization is complete and substrate reflections are completely suppressed, the limits of optical lithography can be explored through computer simulation. The nominal exposure dose as a function of linewidth under perfect focus conditions for three combinations of numerical aperture and exposure wavelength is shown in Fig. 9. Curves a and b use parameters that roughly correspond to existing projection equipment. Curve c simulates a ficticious projection aligner that has an imaging lens with a numerical aperture of 0.25 and an imaging wavelength of 240 nm. The sudden rise in exposure dose for the smaller linewidths indicates a regime where IC process latitude degrades sharply. Operation in the crook of this regime is possible if a set of linewidth compensation rules for the larger linewidths is used.

A more explicit view of process latitude is given by Fig. 10 and Fig. 11, which give the fractional linewidth variation as a function of linewidth for a  $\pm 5\%$  and a  $\pm 10\%$  variation in exposure energy. Curves a, b, and c in Fig. 10 and Fig. 11 correspond to curves a, b, and c in Fig. 9. The calculated nominal dose for each linewidth in Fig. 9 was used to generate Fig. 10 and Fig. 11. The curves in Fig. 10 and 11 were calculated assuming a focus error equal to one-half of a "depth of field."

Current optical systems in conjunction with multilayer processing can probably achieve an effective exposure stability in this range. From curve b in both Fig. 10 and Fig. 11,

**Fig. 10.** The fractional linewidth variation ( $\Delta L/L$ ) as a function of linewidth in micrometers for a ±5% variation in exposure energy for the curves of Fig. 9. Each optical system was degraded by  $\lambda/[4(NA)^2]$  of focus error.

**Fig. 11.** The fractional linewidth variation as a function of linewidth for a  $\pm 10\%$  variation in exposure energy for the curves of Fig. 9.

a projection aligner with a numerical aperture of 0.35 and an imaging wavelength of 405 nm should be able to print a 0.8- $\mu$ m linewidth with 8% to 12% variation in size, using current microfabrication processes. Such an imaging system is commercially available today. As the imaging and alignment systems of optical lithographic equipment improve during the 1980s, production of VLSI circuits with submicrometer design rules should become a reality.

#### References

1. J.D. Cuthbert, Solid State Technology, Vol. 20, August 1977, p. 59.

2. W.G. Oldham, et al, IEEE Transactions on Electron Devices, Vol. ED-26, 1979, p. 717.

3. F.J. Dill, et al, IEEE Transactions on Electron Devices, Vol. ED-22, 1975, p. 445.

4. J.M. Moran and D.M. Maydan, Journal of Vacuum Science and Technology, Vol. 16, 1979, p. 1620.

5. J.H. Bruning, Journal of Vacuum Science and Technology, Vol.17, 1980, p. 1147.

6. K.L. Tai, et al, Journal of Vacuum Science and Technology, Vol. 17, 1980, p. 1169.

7. K.L. Tai, et al, Journal of Vacuum Science and Technology Vol. 16, 1979, p. 1977.

8. B.J. Lin, Journal of the Electrochemical Society, Vol. 127, 1980, p. 202.

9. B. Carlson and J. Arnold, presented at the Kodak Microelectronics Seminar, San Diego, California, October 1980.

G.W. Ray, et al, "Spin-On Glass as an Intermediate Layer in a Tri-Layer Resist Process," Accelerated Brief Communications, Journal of the Electrochemical Society, Vol. 129, September 1982.

M.M. O'Toole and W.J. Grande, IEEE Electron Device Letters, Vol. EDL-2, December 1981, p. 311.

12. D. Meyerhofer, IEEE Transactions on Electron Devices, Vol. ED-27, 1980, p. 921.

13. M.M. O'Toole, E.D. Liu, and M.S. Chang, presented at SPIE Semiconductor Microlithography VI, San Jose, California, March 1981.

14. J.Wilcynski, "Optical Projection Printing—Maturing Technology for the 1980s," presented at the 161st Meeting of the Electrochemical Society, Montreal, Canada, May 1982.

15. M.S. Chang, et al, Journal of Vacuum Science and Technology, Vol. 16, no. 6, November/December 1979, pp. 1973-1976.

#### Gary W. Ray

Gary Ray received a PhD degree in chemical physics from Michigan State University in 1978 and did postdoctoral research at the Jet Propulsion Laboratory of the California Institute of Technology. His research work resulted in several papers on stratospheric chemical kinetics. He joined HP in 1981 and is studying plasma etching. Gary is married, has a daughter, and lives in Mountain View, California. His interests include backpacking, classical music, and early musical instruments.

#### E. David Liu

David Liu joined HP in 1979 with two years of experience in IC photolithography processing. He is now working on electron beam lithography and has co-authored three papers related to microlithography. David received a BS degree in chemistry from National Taiwan University in 1970 and a PhD degree in chemistry from the University of Chicago in 1976. He is a member of the American Vacuum Society, the Electrochemical Society and the Society for Photo-Optical Instrumentation Engineers. He is married, lives in Mountain View, California, and enjoys readina

#### Michael M. O'Toole

Mike O'Toole is the leader of HP Laboratories' trilayer resist implementation project. He came to HP in 1979 after receiving a PhD degree in electrical engineering from the University of California at Berkeley. He has authored or co-authored nine papers on optical lithography and is a member of the IEEE and the Optical Society of America. Mike was born in Los Angeles, California, and now lives in San Jose, California. He has a private pilot's license and enjoys scuba diving.

# Silicon Integrated Circuits Using Beam-Recrystallized Polysilicon

Melting a polysilicon layer by using an intense laser or electron beam can significantly improve the properties of the layer for semiconductor device fabrication. Novel vertical device structures can also be formed with this technique.

#### by Theodore I. Kamins

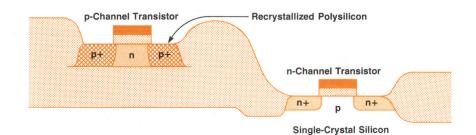

HE RECENT FABRICATION of metal-oxide-semiconductor (MOS) devices in layers of laser- or electron-beam-recrystallized polysilicon<sup>1,2,3</sup> offers the possibility of freeing integrated circuit structures from the constraints of conventional, single-crystal silicon technology.

While transistors fabricated in fine-grain polysilicon have marginally useful characteristics,<sup>4</sup> the behavior of devices in recrystallized polysilicon can approach that of transistors in single-crystal silicon. The new technology offers the promise of high-performance integrated circuits (ICs) fabricated on potentially inexpensive or insulating substrates,<sup>5</sup> as well as the possibility of additional levels of devices on monolithic silicon ICs. Combining levels of recrystallized polysilicon with single-crystal silicon can lead to novel vertical structures,<sup>6</sup> as well as increased component density.

This paper describes the characteristics of recrystallized polysilicon that make it useful for transistor fabrication and the behavior of the resulting devices. A recently fabricated complementary metal-oxide-semiconductor (CMOS) structure that incorporates these transistors is discussed along with potential future applications in three-dimensional integrated circuits and other uses.

#### **Transistors in Recrystallized Polysilicon**

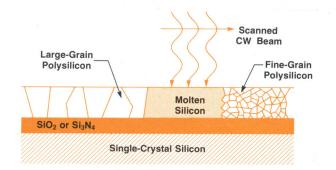

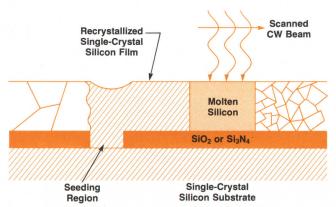

During the past decade sporadic efforts have been made to fabricate MOS transistors with their active channels in layers of polysilicon<sup>4,7</sup> to allow additional flexibility in IC design and fabrication. However, transistors in fine-grain polysilicon have limited application because their threshold voltages are high and their carrier mobilities are low.<sup>4</sup> The transistor characteristics are limited by defect states primarily associated with the many polysilicon grain boundaries. If the number of grain boundaries and associated defect states can be greatly reduced, the transistor properties also improve. To reduce the number of boundaries, the grain size can be increased by melting the fine-grain polysilicon with a scanning, continuous-wave (CW) laser or electron beam (Fig. 1) so that it recrystallizes into large-grain material upon cooling.<sup>8</sup> The transistors fabricated in such material have characteristics approaching those of transistors in single-crystal silicon.

Hewlett-Packard's transistor-fabrication efforts in beamrecrystallized polysilicon have used techniques compatible with high-density, high-performance, MOS IC technology. Consequently, the transistors are fabricated with a state-ofthe-art isolation process using local oxidation of silicon (LOCOS) suitably modified to account for the largegrain structure of the polysilicon.<sup>2,3</sup>

In the most straightforward demonstration of the transistor characteristics, devices are fabricated in polysilicon films deposited on silicon wafers uniformly covered with

**Fig. 1.** As an intense laser or electron beam scans across fine-grain polysilicon, the material melts, and then, as it cools, recrystallizes into large-grain polysilicon.

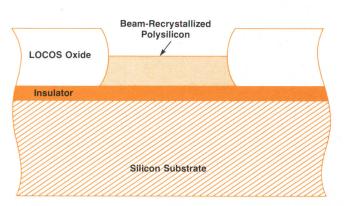

**Fig. 2.** By oxidizing through the entire thickness of the exposed polysilicon areas, the recrystallized polysilicon is separated into isolated device regions surrounded by insulating films.

insulating layers. The polysilicon is melted using an argon-ion CW laser to convert the initial fine-grain polysilicon to large-grain material (Fig. 1). A layer of silicon nitride is deposited over a thin stress-relief oxide layer and patterned to retain the nitride in the active device regions. The exposed polysilicon areas are oxidized until the growing oxide reaches the insulating layer beneath the polysilicon. Each device island of polysilicon is thus completely isolated from adjacent islands and from the substrate by insulating layers (Fig. 2). Alternatively, the polysilicon between device islands could be removed by etching.

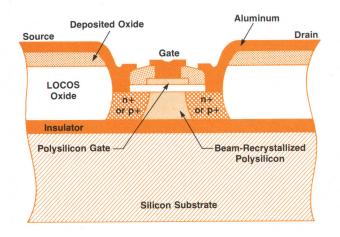

The remaining steps of the transistor-fabrication process are similar to those used to form silicon-gate transistors in single-crystal silicon. A schematic cross section of a finished transistor is shown in Fig. 3. In some cases, the threshold voltage is adjusted by implanting boron or phosphorus through the gate oxide before the gate polysilicon is deposited. Ion-implanted source and drain regions are used and the heat treatment after these implantations is limited to avoid excessive diffusion.

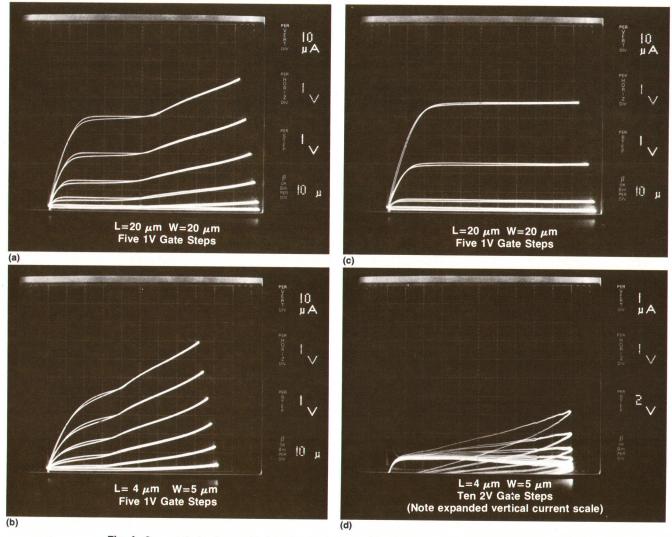

Fig. 4 shows the source-drain characteristics of large- and small-geometry, n-channel, recrystallized polysilicon transistors, as well as single-crystal-silicon and fine-grain polysilicon devices. The kink in the current-versus-voltage characteristic arising from the presence of the insulator under the channel region is clearly seen for the large-geometry transistor. Some p-channel transistors have also been fabricated, and transistors with effective channel lengths as short as 1  $\mu$ m have been obtained. Transistors in polysilicon recrystallized using an electron beam have characteristics similar to those in laser-recrystallized polysilicon.<sup>3</sup>

#### Use of Beam-Recrystallized Devices in Silicon ICs

The characteristics of recrystallized polysilicon transistors can be useful in many IC applications that normally use single-crystal-silicon transistors. The carrier mobilities are generally about half those of single-crystal transistors, but about five to twenty times larger than those of transistors in fine-grain polysilicon (Table I). The threshold voltages of the recrystallized transistors are only slightly greater than those of single-crystal transistors, rather than being 10 or

**Fig. 3.** Schematic cross section of a transistor fabricated in recrystallized polysilicon.

| Table I                                          |

|--------------------------------------------------|

| Characteristics of MOS Transistors Fabricated in |

| Single-Crystal Silicon and Polysilicon           |

|                                  | n-Channel             |                       | p-Channel             |                           |

|----------------------------------|-----------------------|-----------------------|-----------------------|---------------------------|

|                                  | Mobility<br>(cm²/V-s) | V <sub>T</sub><br>(V) | Mobility<br>(cm²/V-s) | V <sub>T</sub><br>(V)     |

| Single-crystal silicon           | 670                   | 1                     | 180                   | -1.5                      |

| Laser-recrystallized polysilicon | 300                   | 1 to 2                | 120                   | -2                        |

| Fine-grain polysilicon           | ≈10 to 20             | ≈10<br>to 20          | ≈20                   | $\approx -10$<br>to $-20$ |

20V higher, as in fine-grain polysilicon transistors. In addition, the source-to-drain leakage current of transistors with short (1 to 2  $\mu$ m) channels is in the range of 10<sup>-13</sup> amperes per micrometer of channel width, not very different from that of single-crystal transistors.

Once discrete transistors and simple ring oscillators had been fabricated in recrystallized polysilicon on silicon wafers uniformly covered with insulating layers, we wanted to combine the polysilicon transistors with those fabricated in adjacent regions of single-crystal silicon. In one potentially beneficial application, p-channel transistors can be fabricated in recrystallized polysilicon and combined with high-performance, n-channel transistors in adjacent regions of the single-crystal silicon substrate to form a CMOS integrated circuit.

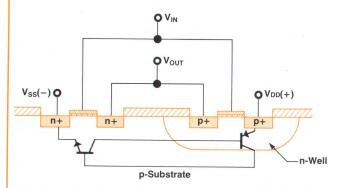

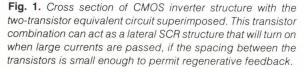

CMOS ICs are becoming increasingly important for the realization of low-power, high-speed functions. While CMOS is generally easy to use, the possibility of latch-up (undesirable large lateral current flow between adjacent complementary devices triggered by some circuit conditions), and the resulting loss of circuit control, may restrict its use. The various techniques that have been used to minimize latch-up may significantly increase the chip size and are, consequently, less than ideal.

Completely separating the two polarities of devices by use of oxide layers totally avoids latch-up, but such complete oxide isolation previously required very difficult processing. Using the new, recrystallized-polysilicon approach, both process simplification and control can be obtained. One type of transistor is fabricated in the singlecrystal substrate, and the other type is formed in a layer of recrystallized polysilicon separated from the single-crystal substrate by an insulating oxide layer.

Placing one type of device in the single-crystal substrate and the other in the polysilicon layer provides the additional advantage of optimizing the characteristics of the most critical transistor. For optimum circuit performance p-channel transistors are fabricated in a layer of laserrecrystallized polysilicon while n-channel transistors are constructed in adjacent regions of the underlying singlecrystal substrate. To simplify the processing and allow the use of existing masks, the transistors are separated laterally, rather than being stacked with a common gate. Fig. 5 schematically shows the cross section of such a transistor

**Fig. 4.** Source-drain characteristics of (a) large-geometry and (b) small-geometry transistors fabricated in recrystallized polysilicon, along with the characteristics of (c) single-crystal-silicon and (d) fine-grain-polysilicon transistors (see reference 2).

pair.

Both n-channel and p-channel, large-geometry transistors exhibit well behaved saturation regions with squarelaw characteristics. Threshold voltages are approximately 1V for the single-crystal, n-channel transistors and -2V for the recrystallized-polysilicon, p-channel transistors. Carrier mobilities are 670 and 120 cm<sup>2</sup>/V-s, as expected for the two types of transistors.

Several different, fifteen-stage ring oscillators were fabricated. Their oscillation periods agree well with the times calculated to charge the capacitance associated with switching a stage. These switching times were calculated from the transistor geometries of each different ring oscillator and the characteristics of discrete transistors. Some of the capacitances that must be charged are markedly lower than in single-crystal circuits because the oxide under the p-channel transistors has a dielectric constant one-third that of silicon.

#### **Future Trends**

Future efforts can be directed along several paths. Dem-

onstration of integrated circuits with transistors in the single-crystal silicon substrate and in layers of recrystallized polysilicon opens the possibility of significantly increased component density, as well as removing some circuit performance limitations (e.g., eliminating the possibility of latch-up in CMOS structures). In addition to improved density, novel structures can be obtained by using interactions in the vertical direction. For example, CMOS gates have been fabricated with a single gate electrode controlling a transistor of one type in the underlying single-crystal substrate and a transistor of the opposite type in recrystallized polysilicon above the gate electrode.<sup>6</sup> The extension to other novel, vertical IC structures offers exciting possibilities for "vertical integration."

Although the transistors in recrystallized polysilicon have characteristics approaching those of single-crystal transistors, the few remaining grain boundaries can limit device performance. Removing these grain boundaries by seeding the regrowth of the silicon layer through periodic contact between the polysilicon and the underlying single-

**Fig. 5.** Schematic cross section of a CMOS transistor pair used in an integrated circuit. Any possibility of latch-up is avoided by completely surrounding one type of transistor by insulating silicon dioxide.

crystal substrate (Fig. 6) can enhance the transistor performance.  $^{9,10}$

Fabricating MOS transistors with their channels in recrystallized polysilicon offers the most exciting and potentially useful application of beam-recrystallization technology. However, several more-straightforward applications should be mentioned. The ease of implementing these would lead to a more immediate impact on IC technology. For example, recrystallization of polysilicon may make the resistivity of high-valued resistors used in static RAMs less sensitive to slight variations in dopant concentration.<sup>11</sup> Melting only the top region of a polysilicon layer may smooth its surface, allowing the formation of higher-quality thermal oxides for double-level polysilicon-gate MOS ICs.<sup>12</sup> Finally, the use of other heat sources to melt the polysilicon, such as black-body radiation,<sup>13,14</sup> may simplify recrystallization.

#### Acknowledgments

The author would like to thank D. Ilic, F. Schwettmann, and J. Moll for their ideas and encouragement during this investigation and the other members of the beamrecrystallization project: C. Drowley, P. Zorabedian, and C. Heimberg.

#### References

1. K.F. Lee, et al, "Thin Film MOSFETs Fabricated in Laser-Annealed Polycrystalline Silicon," Applied Physics Letters, Vol. 35, July 15, 1979, p. 173.

2. T.I. Kamins, et al, "A Monolithic Integrated Circuit Fabricated in Laser-Annealed Polysilicon," IEEE Transactions on Electron Devices, Vol. ED-27, January 1980, p. 290.

3. T.I. Kamins and B.P. Von Herzen, "MOSFETs in Electron-Beam

**Fig. 6.** Single-crystal regions of silicon are formed by "seeding" the regrowth of a polysilicon layer using periodic contact between the layer and the underlying, single-crystal substrate. Recrystallized Polysilicon," IEEE Electron Device Letters, Vol. EDL-2, December 1981, pp. 313-315.

4. T.I. Kamins, "Field-Effects in Polycrystalline-Silicon Films," Solid-State Electronics, Vol. 15, 1972, pp. 789-799.

5. T.I. Kamins and P.A. Pianetta, "MOSFETs in Laser-Recrystallized Polysilicon on Quartz," Electron Device Letters, Vol. EDL-1, October 1980, pp. 214-216.

6. J.P. Colinge and E. Demoulin, "A High-Density CMOS Inverter with Stacked Transistors," IEEE Electron Device Letters, Vol. EDL-2, October 1981, pp. 250-251.

7. C.H. Fa and T.T. Jew, "The Polysilicon Insulated-Gate Field-Effect Transistor," IEEE Transactions on Electron Devices, Vol. ED-13, February 1966, pp. 290-291.

8. A. Gat, et al., "CW Laser Anneal of Polycrystalline Silicon: Crystalline Structure, Electrical Properties," Applied Physics Letters, Vol. 33, October 15, 1978, p. 775-778.

9. M. Tamura, H. Tamura, and T. Tokuyama, "Si Bridging Epitaxy from Si Windows onto SiO<sub>2</sub> by Q-Switched Ruby Laser Pulse Annealing," Japanese Journal of Applied Physics, Vol. 19, January 1980, pp. L23-26.

10. T.I. Kamins, et al, "Lateral Epitaxial Recrystallization of Deposited Silicon Films on Silicon Dioxide," Journal of the Electrochemical Society, Vol. 128, May 1981, pp. 1151-1154.

11. G. Yaron, L.D. Hess, and G.L. Olson, "Electrical Characteristics of Laser-Annealed Polysilicon Resistors for Device Applications," in *Laser and Electron Beam Processing of Materials*, edited by C.W. White and P.S. Peercy, Academic Press, 1980, pp. 626-631.

12. G. Yaron, L.D. Hess, and S.A. Kokorowski, "Application of Laser Processing for Improved Oxides Grown from Polysilicon," IEEE Transactions on Electron Devices, Vol. ED-27, May 1980, pp. 964-969.

13. J.C.C. Fan, M.W. Geis, and B.-Y. Tsaur, "Lateral Epitaxy by Seeded Solidification for Growth of Single-crystal Si Films on Insulators," Applied Physics Letters, Vol. 38, March 1, 1981, pp. 365-367.

14. B.-Y. Tsaur, et al, "Improved Techniques for Growth of Large-Area Single-Crystal Si Sheets Over SiO<sub>2</sub> Using Lateral Epitaxy by Seeded Solidification," Applied Physics Letters, Vol. 39, October 1, 1981, pp. 561-563.

#### **Theodore I. Kamins**

Ted Kamins is an author or co-author of 52 articles, many on polycrystalline silicon. He is a co-author of a book, *Device Electronics for Integrated Circuits*, and is named inventor on five patents related to IC technology. Ted joined HP in 1974 with several years of experience in materials and device R&D work. He is a project leader in the Integrated Circuit Laboratory of HP Laboratories. Ted holds BS (1963), MS (1964), and PhD (1968) degrees in electrical engineering awarded by the University of California at Berkeley, where he has held the position of acting assistant professor. He has also served as a visiting lecturer at Stanford University. Ted is a member of the Electrochemical Society and a Senior Member of the IEEE.

## X-Ray Lithography

The shorter wavelengths of soft X-ray radiation make the definition of even smaller dimensions for VLSI circuits possible.

#### by Garrett A. Garrettson and Armand P. Neukermans

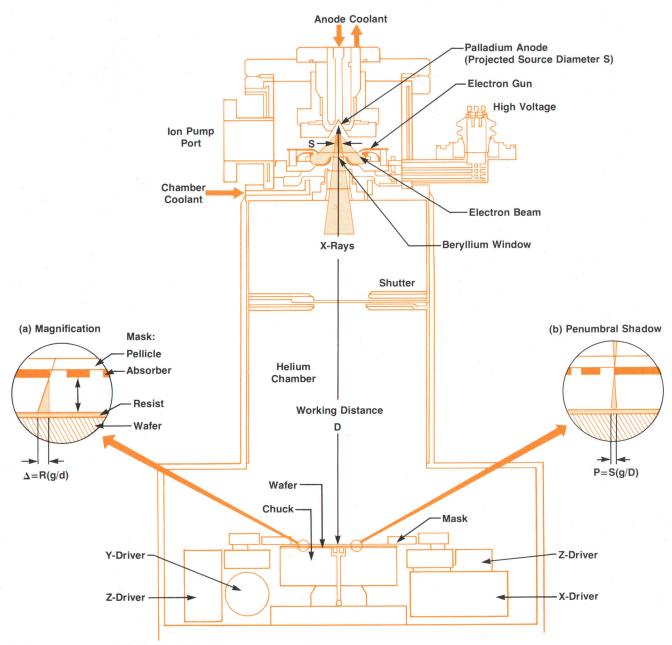

-RAY LITHOGRAPHY is proximity printing using a quasi-point source of soft (0.25 to 3.0 keV) X-rays. The important elements of an X-ray exposure system are illustrated in Fig. 1. X-rays are generated in an evacuated area by electron bombardment and penetrate a thin (25 to 50  $\mu$ m) beryllium window. They are shadowed by a mask consisting of an absorber pattern supported on a flat membrane (5 to 10  $\mu$ m thick) that is relatively transparent to the radiation. The mask is accurately positioned parallel to the wafer and in close proximity (typically 10 to 100  $\mu$ m) with it. The wafer is coated with an X-ray-sensitive resist. The space between the X-ray source and the mask (working distance D) is evacuated or filled with helium to reduce attenuation of the radiation.

#### X-Ray Source

High-energy (10 to 30 keV) electron bombardment sources are commonly used to generate the required soft X-ray radiation. Other sources such as synchrotron radiation, plasma pinch, and laser plasmas are being considered, but presently their application to integrated circuit lithography is either prohibitively expensive or needs further development.

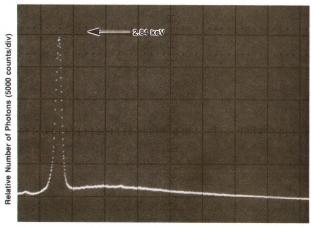

A typical measured spectrum from 20-keV electron bombardment of palladium (Pd) is illustrated in Fig. 2. The desired characteristic radiation under the peak (2.84 keV) is caused by electronic transitions in the  $L_{\alpha}$  shell of a palladium atom. The remaining continuum spectrum is caused by the deceleration of electrons interacting with the Pd target atoms. Although the continuum spectrum does provide some additional exposure energy, its predominantly higher-energy X-rays are weakly absorbed, tending to produce an undesirable reduction of exposure contrast. Maximum source brightness (maximum power and minimum spot size) are factors determined by the electron optics, the characteristics of the anode (melting point, vapor pressure, elastic strength), and the performance of the cooling system.

#### **Mask and Resist**

The X-ray mask is the most critical structure in the system. The membrane (pellicle) supporting the absorber pattern must be made of a thin, low-atomic-number material to minimize X-ray attenuation, and yet must remain stable to minimize distortions caused by stresses in the absorber pattern. Typically the pellicle is stretched across a stiff, flat ring whose expansion coefficient matches that of silicon. This is essential to achieve good gap control between the mask and the wafer and to alleviate the requirement for absolute temperature control. To first order, the absorber pattern and the wafer should expand and contract at the same rate.

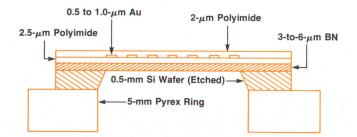

A typical mask structure is shown in Fig. 3. Factors important to mask fabrication are pattern accuracy, absorber line-edge profile, and defect density.

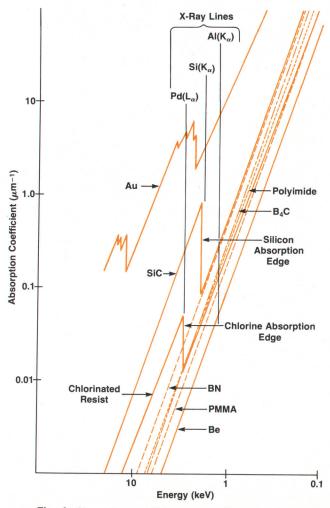

Whereas for optical masks the transmission through clear and opaque areas may differ by orders of magnitude, for X-ray masks the transmission may only differ by approximately a factor of ten. For good contrast the absorber material is made as thick as possible (typically 0.1 to 1.0  $\mu$ m of gold). Hence submicrometer linewidths result in absorber pattern aspect ratios (thickness divided by lateral dimension) approaching unity, which require considerable expertise in fabrication. A careful tradeoff must be made among the source energy spectrum, mask transmission and contrast, and absorption in the X-ray resist.

Presently, for state-of-the-art integrated circuit lithography (minimum feature size of 0.5 to 1.0  $\mu$ m), the combination of Pd-L $_{\alpha}$  radiation, a boron-nitride mask pellicle, a gold absorber pattern, and a resist containing chlorine appears most effective. The fortuitous position of the Pd-L $_{\alpha}$  peak with respect to the chlorine absorption edge (Fig. 4) and the symbiotic effect of this halogen, which increases both absorption and resist speed, make a powerful combination.<sup>1</sup> For higher-resolution lithography, characteristic radiation softer than Pd-L $_{\alpha}$  can be used to reduce the required absorber thickness and increase absorption in the resist at the expense of reduced X-ray energy at the wafer.

#### Alignment

Given an accurate mask pattern there must be a consistent mechanical means for positioning it with respect to the wafer to insure level-to-level alignment accuracy. This requires position references on the mask and on the wafer, as well as an alignment scheme. As illustrated in Fig. 1b, the mask-to-wafer gap can be adjusted to compensate for linear distortion of the wafer or the mask caused by processinduced strain. This is a significant advantage that allows good layer-to-layer alignment over larger fields than would be possible otherwise. Reproducible mask-to-wafer gap control is essential for accurate alignment. For this reason the mask plane must be flat to better than a micrometer and the wafer topography must be kept consistent each time the wafer is pulled down on the vacuum chuck. Dirt between the chuck and the wafer can result in surface bumps unless the chuck is designed to minimize the contact area. For this

**Fig. 1.** Basic X-ray lithography system. Close-up views of mask-to-wafer cross section showing (a) magnification and (b) penumbral shadow errors.

reason a "bed-of-nails" design using many small contact areas is preferred.<sup>2</sup>

#### Tradeoffs

The perceived advantages of X-ray lithography have been its extreme fine-line capability (because of the absence of diffraction and proximity effects<sup>3</sup>), uniform resist exposure that allows high resist aspect ratios, good linewidth control, and insensitivity to dirt. As the field develops the perception of the strengths of X-ray lithography relative to other microlithographic technologies is evolving.

There have been dramatic improvements in the last five years in the performance of optical lithography, principally through the use of projection/reduction steppers and multilevel resist technologies. This performance comes, however, at considerable capital expense, reduced throughput, and increased processing complexity. The investment for an X-ray system is projected to be a fraction of that required for an optical stepper. Although many of the technologies involved are not easy to master, they are not necessarily expensive in their execution. High throughput is projected (20 to 100 wafer levels an hour), because of large subfields and relatively short exposure times (down to 20 seconds using a 4-kW source).<sup>4</sup> Less stringent environmental requirements and the potential for using single-level resists are additional advantages.

In a recent study, Lepselter computed a figure of merit for various lithographic systems, which included such factors

Energy (1.83 keV/div)

Fig. 2. X-ray spectrum for palladium target excited by 20-keV electrons.

as useful resolution, throughput, cost, and clean room footprint (floor space required). He concluded that X-ray lithography's potential merit is at least ten times that of any other submicrometer lithographic technology.<sup>5</sup> His study, however, does not take into account the various difficulties in making appropriate masks, which are crucial. Fabrication of accurate, defect-free  $5 \times$  and  $10 \times$  recticles is easier than fabrication of the  $1 \times$  masks required for X-ray lithography. The physical barriers inherent in pushing optical systems to their limits are traded for the technological problems of X-ray-mask fabrication. Many steps in X-ray-mask fabrication are similar to those used in wafer processing, but the inherent defect densities of these processes must be decreased. On the other hand, considerable progress is being made in improving mask stability, formerly the principal concern.6

X-ray lithography also requires new sensitive resist systems that are just beginning to become available. Source brightness and resist sensitivity will determine the system throughput capability.

Initially, X-ray lithography will complete with optical projection direct-step-on-wafer (DSW) technology. Optical DSW performance is limited by cost, throughput, susceptibility to the environment, and by tradeoffs among resolu-

Fig. 3. Cross section of typical X-ray mask structure.

tion, field size, and depth of focus. Registration for X-ray lithography appears easier to do than for optical lithography because of the magnification correction and the close proximity of the mask to the wafer.

As linewidths continue to shrink a regime will be reached where only X-ray stepper and electron beam technologies are viable. X-ray lithography can be considered a complementary extension of the electron beam pattern generator. It can accurately replicate submicrometer patterns with good linewidth control, which is necessary for consistent MOS device thresholds.

#### Hewlett-Packard X-Ray Program

The objective of the present Hewlett-Packard Laboratories program is to demonstrate a complete X-ray lithography technology that will be simple, high-performance, and cost-effective for submicrometer devices in VLSI circuit production. The current goal is to establish a state-ofthe-art capability at HP Laboratories for mask technology and process development so that X-ray lithography can mature to a level suitable for use in HP's production facilities.

In order of priority, HP has been developing an X-raymask fabrication and precision mask-to-wafer alignment

Fig. 4. Absorption coefficient versus X-ray wavelength for several materials.

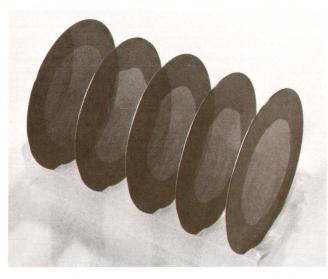

Fig. 5. Photo of boron-nitride pellicles.

capability, fast resist systems, a bright X-ray source, and laboratory exposure tools. The first-generation mask technology uses a pellicle of chemical-vapor-deposited boron nitride and polyimide supporting a sputter-etched gold absorber pattern (Fig. 3 and Fig. 5). This is bonded to a Pyrex<sup>TM</sup> ring for mechanical and thermal stability. Initial tests indicate that presently the stability is adequate for design rules down to one micrometer. Other materials such as silicon carbide and boron carbide have been investigated for the mask pellicle and they show considerable promise for future applications.

Defect density remains a critical problem. With careful process control, defects have been reduced around two orders of magnitude in the past year. Two orders of magnitude more will be required for VLSI.

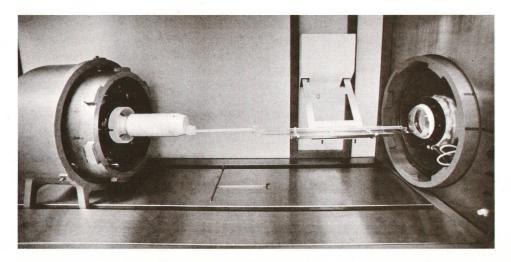

A number of fast, chlorinated, negative resists have been evaluated. Fig. 6 (page 18) shows submicrometer features in 0.6 to 0.8  $\mu$ m of remaining resist material that has been exposed about 4 minutes using a 4-kW source at a working distance of 35 centimeters. A fixed anode source of a modified Gaines design<sup>7</sup> has been built (Fig. 1). With a proprietary cooling technology it appears that power densities greater than 40 kW/cm<sup>2</sup> may be accommodated.

Several laboratory exposure systems have been built for evaluating resists, for mask development, and ultimately for IC applications. The latest is a very compact automaticalignment exposure system employing a novel mask-towafer positioning system with six degrees of freedom. A proprietary alignment scheme can resolve misalignments as small as 20 nanometers consistently, but the level-tolevel alignment accuracy of the system has yet to be determined under realistic operating conditions.

#### **Acknowledgments**

The authors acknowledge the support of their colleagues in the Physical Electronics and Solid-State Laboratories of Hewlett-Packard Laboratories and thank them for their contributions to the work described in this article.

#### References

1. A. Zacharias, "An X-Ray Lithography System for VLSI Device Fabrication," American Vacuum Society Proceedings: 15th Symposium on Electron, Ion, and Photon Beam Technology, Boston, Massachusetts, 1979, p. 1953.

2. T.E. Saunders, "Wafer Flatness Utilizing the Pin-Recess Chuck," Solid State Technology, Vol. 25, no. 5, May 1982, pp. 73-76.

3. P. Rissman and M.P.C. Watts, "Proximity Effect Correction by Means of Processing: Theory and Applications," Hewlett-Packard Journal, Vol. 32, no. 12, December 1981.

4. H. Levinstein, Extended Abstracts, 161st Meeting of the Electrochemical Society, Vol. 82-1, Montreal, Canada, May 1982, p. 281.

5. The Rosen Electronics Letter, February 8, 1982, p. 7.

6. B. Triplet and S. Jones, "X-Ray Lithography: Fabrication of Masks and VLSI Devices," Society of Photo-Optical Instrumentation Engineers Proceedings 333, San Jose, California, March 1982.

7. J. L. Gaines, Nuclear Instrumentation Methods, Vol. 102, 1972, pp. 7-12.

#### Armand P. Neukermans

Armand Neukermans is a project manager for X-ray lithography at HP Laboratories. Born in Okegem, Belgium, he received his BSME and BSEE degrees from Louvain University in 1962, did engineering work for the next five years, and then returned to school, receiving his MSEE degree from Arizona State University (1967) and PhD degree in applied physics from Stanford University (1970). After three years of xerographic research, Armand joined HP in 1973. Among his contributions are a cesium iodide X-ray imaging screen, an electron capture detector for

gas chromatography, and work on Monte Carlo simulations for electron beam exposures. His work has resulted in ten patents and 13 papers. He is a member of the IEEE and Sigma Xi. Armand is married, has four children, and lives in Palo Alto, California. He teaches religious education and enjoys jogging, swimming, and hiking.

#### Garrett A. Garrettson

Garry Garrettson is a native of California born in San Francisco. He attended Stanford University, earning the BS (1965) and MS (1966) degrees in engineering physics and the PhD (1969) degree in mechanical enginering. After a few years as an assistant professor at the U.S. Naval Postgraduate School, Garry joined HP Laboratories in 1973. Since then he has worked in areas of metrology, medical instrumentation, and photoconductor development. Garry presently is a department manager in the Physical Electronics Laboratory of HP Laboratories and has

responsibility for lithography strategy and X-ray technology development. He is the author or co-author of six publications related to transport theory and lithography. Garry served several years in the U.S. Navy, attaining the rank of lieutenant. He is a member of the American Physical Society and the American Association for the Advancement of Science. He is married, has two children, and lives in Los Altos Hills, California. Outside of work, Garry coaches soccer and baseball and supports a Cub Scout group. He enjoys running, skiing, carpentry, and flying (he has a commercial pilot's license with an instrument rating).

¥

1

**Fig. 6.** Patterned results in fast negative resist using X-rays from Pd anode excited by 10-keV electrons, a 25-μm-thick beryllium window, and a mask-to-wafer gap of 25 μm.

## **Dry Etching: An Overview**

Plasma etching technology has several advantages for IC processing compared to wet-chemical etching methods. Anisotropic etching and automatic endpoint detection are two of the advantages discussed in this article.

#### by Paul J. Marcoux

NE OF THE BASIC TRENDS in silicon integrated circuit process technology is the shrinking of device geometries. Recent advances in lithography allow the patterning of feature sizes sufficiently small that conventional methods of etching are inadequate. During the past several years dry etching has evolved to the point where this etch process can transfer the lithographic pattern to the device structure with high fidelity.

The process technique of dry etching has many variations. This technology ranges from processes in which the etching proceeds by a purely physical mechanism to cases in which chemical interactions dominate the etch. The most versatile dry etch processes for pattern replication are those in which chemical etching is enhanced by the physical component of the process. Ion milling and sputter etching techniques use momentum transfer from inert-gas ion bombardment as the physical etch mechanism. Reactive ion beam etching (RIBE, also reactive ion milling), reactive ion etching (RIE, also reactive sputter etching) and plasma etching all use reactive ions to transfer momentum to the sample and add a chemical component to the etching process. Table I provides a qualitative comparison of the dry etch technologies and conventional wet etch processing.

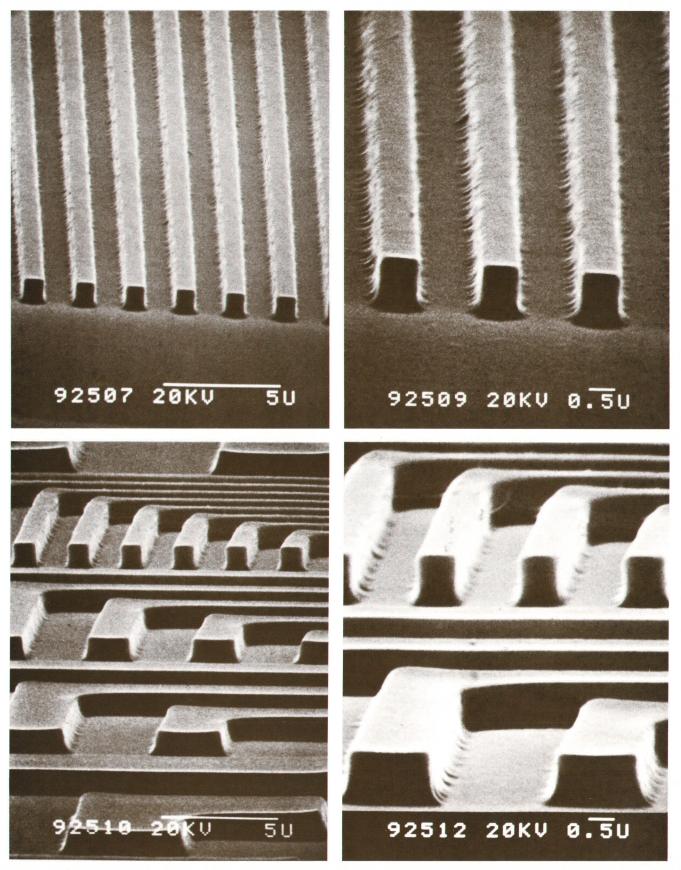

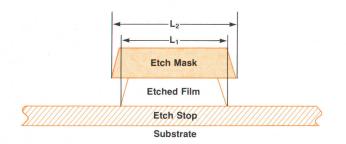

The key process characteristics associated with the plasma etch process are anisotropy and etch selectivity with respect to the photoresist mask and the underlying materials (etch stop). Fig. 1 shows a representation of a typical cross section of an etched sample.

The after-etch profile of a feature is the critical result of the plasma etch process. This profile indicates whether or not a particular etch process gives an isotropic (uniform in all directions) or anisotropic (direction-dependent) etch. In

**Fig. 1.** A typical cross section of an integrated circuit feature. For an anisotropic etch  $L_1 = L_2$  and  $L_2$  is not altered by the etch process. In most processes the ratio of the film etch rate to the etch-stop-material etch rate varies from 5:1 to 10:1. The ratio of the film etch rate to the mask etch rate is similar.

#### Table I

#### A Qualitative Comparison of Etching Methods for Silicon Integrated Circuit Fabrication

|                 | Physical<br>Etching                | Plasma-Assisted<br>Etching          | Wet<br>Etching    |

|-----------------|------------------------------------|-------------------------------------|-------------------|

| Process:        | Ion milling,<br>sputter<br>etching | RIBE, RIE, plasma                   | Wet<br>chemical   |

| Mechanism:      | Momentum<br>transfer               | Ion-assisted<br>chemical reaction   | Chemical reaction |

| Selectivity:    | Poor<br>(≈2 to 3:1)                | Fair (≈5:1) to<br>excellent (>30:1) | Excellent         |

| Directionality: | Anisotropic                        | Anisotropic/isotropic               | Isotropic         |

Fig. 2 isotropic and anisotropic etch profiles are compared. For processes that produce an isotropic etch profile the reduction of linewidth is at least twice the film thickness. Since the linewidths of minimum-size features are typically two to four times the film thickness it is obvious why an isotropic etch is not useful. The only way to reproduce fine-line lithography is to use an anisotropic etch. Another important feature of an anisotropic etch is that generally there is no increased loss of linewidth control with overetching. This is important because overetching is required in routine processing to ensure that all wafers in a load have been completely cleared during the etch process.

In ion milling and sputter etching, inert gas ions bombard the surface of the wafer and sputter away the surface atoms via momentum transfer. In ion milling, ions are extracted from an ion source, accelerated, and deionized before impacting the surface being milled. In sputter etching, ions that bombard the surface are extracted from the gas glow discharge in which the wafers are immersed. In both of these methods the etching is quite anisotropic because the motion of the ions follows electric field lines that are perpendicular to the substrate. The etch selectivity for these processes is generally poor because the sputter yields for materials used in integrated circuit fabrication are similar. In addition, there is often redeposition of the sputtered material along the sidewalls of the lithographically defined pattern. In spite of these disadvantages these technologies are useful, particularly in the laboratory, because they can be used to pattern fine lines in a wide range of materials.

Reactive ion beam etching is an emerging technology that

is similar to ion milling except that the ions responsible for the sputtering action are also reactive. This approach has the advantage that the material being etched can be converted to a volatile compound as well as sputtered. At this time this technology is mainly a laboratory tool. However, if the numerous equipment problems can be overcome it may see broader application.

The techniques of reactive ion etching and plasma etching have the widest range of commercial and laboratory applications. Both etching methods make use of a glow discharge to create the reactive etch species and the ions responsible for the etch process from the input gases. These reactive species and ions diffuse to the substrate surface where they react with the thin film to be etched. This etch reaction must produce a compound that is volatile; otherwise the etch process will be quenched by a residue coating on the surface. It is also very important that the etch reaction be selective with respect to the mask material and the materials under the layer being etched. The principal hardware differences between these two technologies are that in reactive ion etching the substrates are placed on the cathode and the gas pressure is low, while in plasma etching the wafers are placed on the anode and the gas pressure is somewhat higher. In most cases this results in higher ion energies and hence more momentum transferred to the surface in reactive ion etching. Table II lists materials that have been etched using plasma etching at Hewlett-Packard Laboratories. It shows the versatility of this technology and indicates the possible reactive etch species and corresponding volatile etch product for each material.

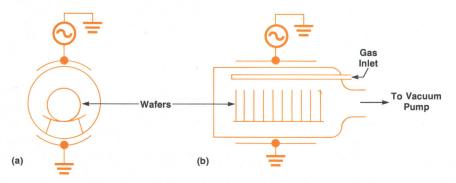

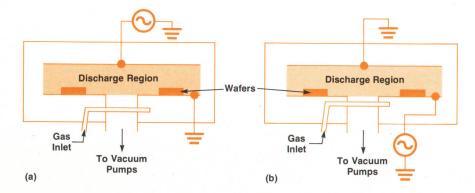

#### Reactors

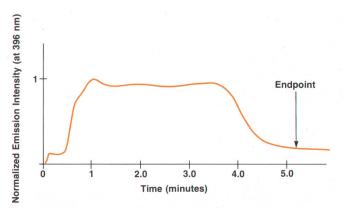

Commercially available plasma etch reactors range from laboratory apparatus to highly automated reactors suitable for use in integrated circuit manufacturing. These reactors are available in two basic configurations: barrel or parallel plate. The selection of the configuration depends upon the user's application. All reactors have the following basic components: reaction chamber, vacuum system, gas flow control, an RF power supply, and in most cases, automatic gas pressure control. In the more sophisticated reactors a microprocessor controls the gas flows, total pressure, and the vacuum values associated with the reactor. In many systems the wafer handling is also automated. An increasing number of reactors have automatic process is complete (see box on page 22).

**Fig. 2.** Comparison of the etch profiles for isotropic and anisotropic etching. (a) Diagram of isotropic etch profile. (b) SEM photograph of actual isotropic profile. (c) Diagram of anisotropic etch profile. (d) SEM photograph of ac-

tual anisotropic profile.

#### Table II

#### Summary of Plasma Etch Processes

| Material<br>Etched             | Etch Gas<br>Composition           | Reactive<br>Species | Principal<br>Etch Products |

|--------------------------------|-----------------------------------|---------------------|----------------------------|

| Resist                         | O2                                | 0                   | O2, H2O, CO2               |

| Si                             | $CF_4 + O_2$                      | F                   | SiF4                       |

|                                | CCl <sub>4</sub> + He             | Cl                  | SiCl <sub>4</sub>          |

| SiO <sub>2</sub>               | C <sub>2</sub> F <sub>6</sub> +He | CF3, F              | SiF4, CO, CO2              |

| Si <sub>3</sub> N <sub>4</sub> | $CF_4+O_2$                        | F                   | SiF4, N2                   |

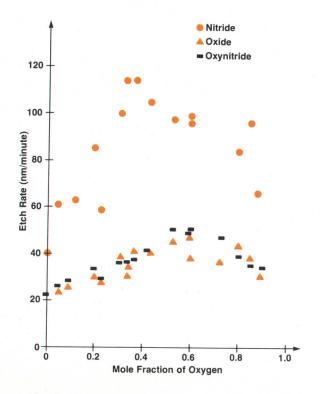

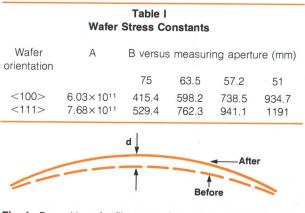

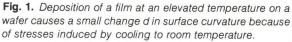

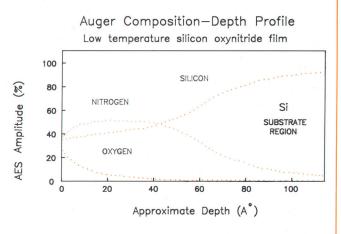

| W                              | $CF_4 + O_2$                      | F                   | WF <sub>6</sub>            |